#### Overcoming Standard Limitations in Synchrophasor Systems

#### **PJM PDC Testing Experience**

Yi Hu, Vasudev Gharpure Quanta Technology LLC

Bill Walker, Jing Liu PJM Interconnection

> Knoxville, TN March 12, 2014

PJM Confidential 777364

- PJM Control Center PDC

- PJM PDC testing objectives

- PDC testing setup

- Tests performed

- Key findings from the testing

- Standard limitations and possible mitigation solutions

- Conclusions

# **⊅**∕pjm

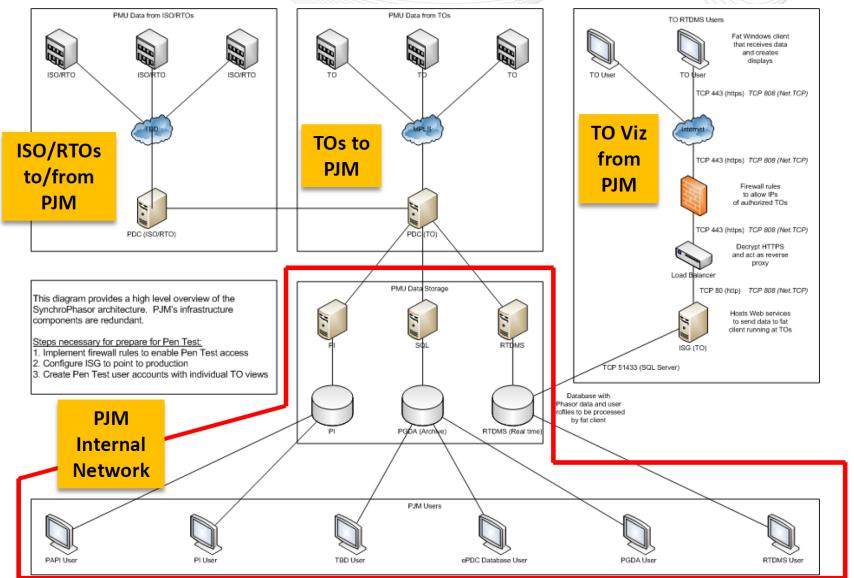

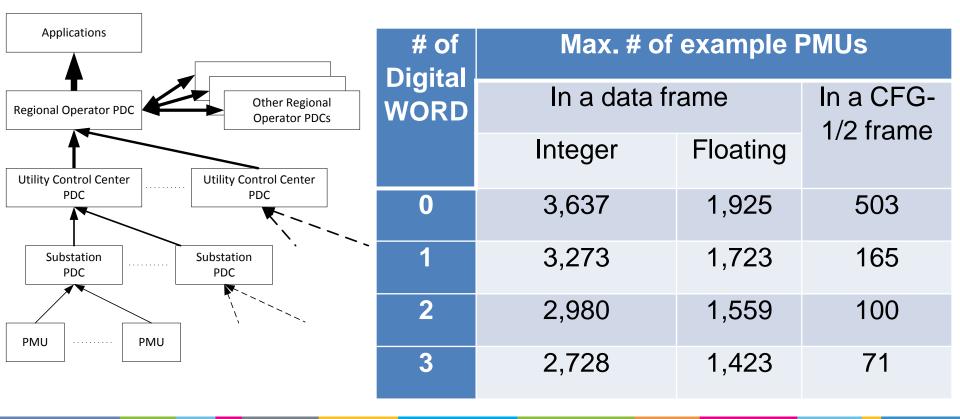

#### PJM SynchroPhasor Architecture

PJM Confidential 777364

PJM Control Center PDCs

### Functional requirements

- Total number of PMUs

- Data from TOs

- Installing 300+ PMUs at 100+ substations

- Building support for 150+ substations

- Data exchange plan PMU data from neighboring ISOs

- MISO: 263 PMUs

- NYISO: 48 substations with PMUs

- Total over 500 PMUs and at least to support twice that in near future

- Data forwarded to

- RTDMS must be in single stream

- PI database must be in single stream?

# Objectives

- Determine if PDC will be able to meet PJM synchrophasor system requirements

- Current needs

- Getting data from all TOs

- Adding time-tag to received data

- Data quality

- Future needs

- Sufficient capacity

- Adequate performance

- Have a clear understanding how PDC works

- Setting status flags

- Output behavior under various input conditions

PJM PDC Testing – cont.

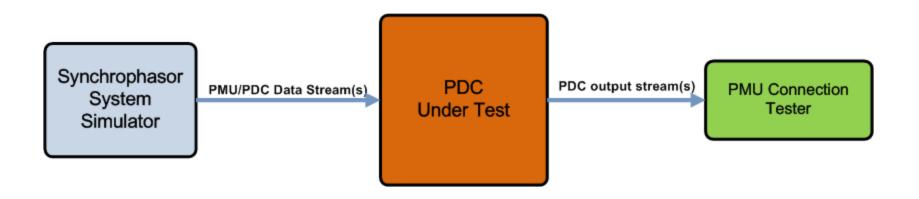

## Test setup

- Synchrophasor system simulator

- Generate various test data streams based on the test case specification

- PMU Connection Tester

- Capture PDC output data for analysis

### Tested scenarios

- Normal condition

- Missing data packets

- Late data arrival

- Flagged PMU data

- Invalid/PMU error

- Lost sync indication

- Sort by arrival

- Trigger flags

- PMU configuration changes

- PMU data frame CRC error

- Time of Arrival check

- Capacity test

Key Findings

### We need PDC standard!

- Size limitation of the standard

- Could be a major issue

- Standardized way for PDCs to respond to

- Setting flags

- Data quality marking

- Processed data indication

- Change management (e.g. Add/remove PMUs from a stream)

- Long interruptions of all input data

Data element size in data and configuration frames

– total bytes must be < 65536 (frame size)</li>

| Data element | Data frame |          | CFG-1/2 frame | CFG-3 frame |

|--------------|------------|----------|---------------|-------------|

|              | Integer    | Floating |               |             |

| Phasor       | 4          | 8        | 20            | 13-268      |

| Analog       | 2          | 4        | 20            | 9-264       |

| Digital      | 2          | N/A      | 260           | 20-4100     |

| Frequency    | 2          | 4        | 0             | 0           |

| df/dt        | 2          | 4        | 0             | 0           |

Standard Limitations – cont.

#### Ultimate limit – One data element per PMU only

| Data element     | Max. # of F<br>a data f | Max. # of<br>PMUs in a<br>CFG-1/2 |       |

|------------------|-------------------------|-----------------------------------|-------|

|                  | Integer                 | Floating                          | frame |

| One phasor only  | 10,913                  | 6,547                             | 1,309 |

| One analog only  | 16,369                  | 10,913                            | 1,309 |

| One digital only | 16,369                  |                                   | 225   |

#### Standard Limitations – cont.

#### A sample PMU

One voltage phasor, two current phasors, two analog values, and zero to three digital WORD

Mitigation Options

There are several options

- Limit data element

- No digital, positive sequence phasors only

- May not meet applications requirement

- Use CFG-3

- Can get some relief

- May not be a long term solution

- Multiple streams

- Can be a solution

- Complication on receiving side

- New standard or standard revision

- Preferred but will take some time

- PDC testing is important to

- Understand how they function

- Whether they can meet system functional and performance requirements, and

- Whether they are interoperable with other system components

- Using synchrophasor system simulator is an effective way to perform such tests

- For large-scale synchrophasor systems, current standard will become a major limitation in transporting synchrophasor data

- Configuration frame CFG-1/CFG-2 is the bottleneck

- There are some mitigation options

- Standardized approach is preferred